1. 什么是UVLO

欠压锁定(Undervoltage-Lockout)简称UVLO,是电子设备中在电源电压低于正常工程准位时,切断电源的电路。在嵌入式系统中常会用UVLO监控电池电压,若电压低于一定值,会直接切断电源,保护嵌入式系统的电路。

许多电子设备中都有UVLO的功能,例如在镇流器中就有UVLO电路,若电压过低时直接切断电源。

欠压锁定(Undervoltage-Lockout)简称UVLO,是电子设备中在电源电压低于正常工程准位时,切断电源的电路。在嵌入式系统中常会用UVLO监控电池电压,若电压低于一定值,会直接切断电源,保护嵌入式系统的电路。

许多电子设备中都有UVLO的功能,例如在镇流器中就有UVLO电路,若电压过低时直接切断电源。

运算放大器(简称“运放”)是具有很高放大倍数的电路单元。在实际电路中,通常结合反馈网络共同组成某种功能模块。它是一种带有特殊耦合电路及反馈的放大器。其输出信号可以是输入信号加、减或微分、积分等数学运算的结果。是电路中的一个常用结构。

运放的结构多种多样,本文记录一种简单的结构

本文记录以二极管连接的MOS作为负载的共源极放大器。

二极管连接的MOS管如下图所示。

无论PMOS还是NMOS,当导通时,均工作在饱和区。

等效电阻为

$$R_x=\frac{V_x}{I_x}=\frac{1}{g_m}//R_o\approx\frac{1}{g_m}$$

以二极管连接的mos作负载的共源极放大器电路连接如下图所示

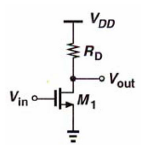

以电阻负载的共源极放大器为例,记录交流小信号分析的方法与过程。

电路基本结构如下图所示

MOS管处于截止区时,$V_{gs}<V_{TH}$

处于饱和区时,$V_{gs}>V_{TH}$且$V_{DS}>V_{gs}-V_{TH}$

处于线性区时,$V_{gs}>V_{TH}$ 且 $V_{DS}<V_{gs}-V_{TH}$

本文主要介绍使用ADE进行直流仿真与分析。

载有电流I半导体棒,如果沿电流方向的电荷密度是Qd,电荷移动速度是v,那么$I=Q_d*V$,Qd可以表示为$Q_d=WC_{Ox}(V_{GS}-V_X-V_{th})$ 则电流可给出 $I_D=WC_{OX}[V_{GS}-V_{(X)}-V_{TH}]$ 。负号是因为载流子电荷为负引入的,v表示沟道电子的漂移速度。电子迁移率用 ,可得到如下结论。

截止区 $I_D\approx0$

线性区 $I_D=\frac{u_nC_{OX}W}{2L}[2(V_{GS}-T_(TH))V_{DS}-V_{DS}^2]$

饱和区 $I_D=\frac{U_NC_{OX}W}{2L}(V_{GS}-V_{TH})^2$

本文主要记录使用ADE进行仿真的过程。

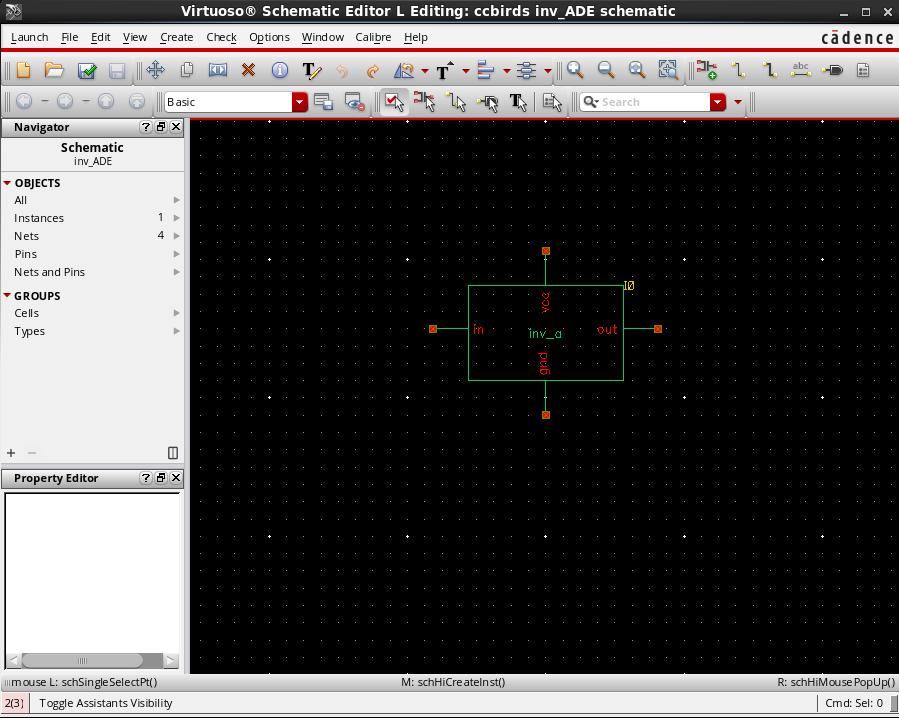

新建一个Cell,填加画好的反相器symbol,如下图所示。

仿真,需要填加电源和信号源,(也可以不加电源和信号源,方法在后面会介绍)。电源和信号源,在analoglib库中,这里面的器都 是理想器件,是不能layout的。电源的cell名为-vdc,电源的电源在下面的DC voltage修改,在这里设置为3.3V,大家根据自己情况设置。加完电源后,需要要加一个gnd,gnd没有参数。